- 您现在的位置:买卖IC网 > Sheet目录327 > HW-V5-ML561-UNI-G (Xilinx Inc)EVALUATION PLATFORM VIRTEX-5

R

Termination and Transmission Line Summaries

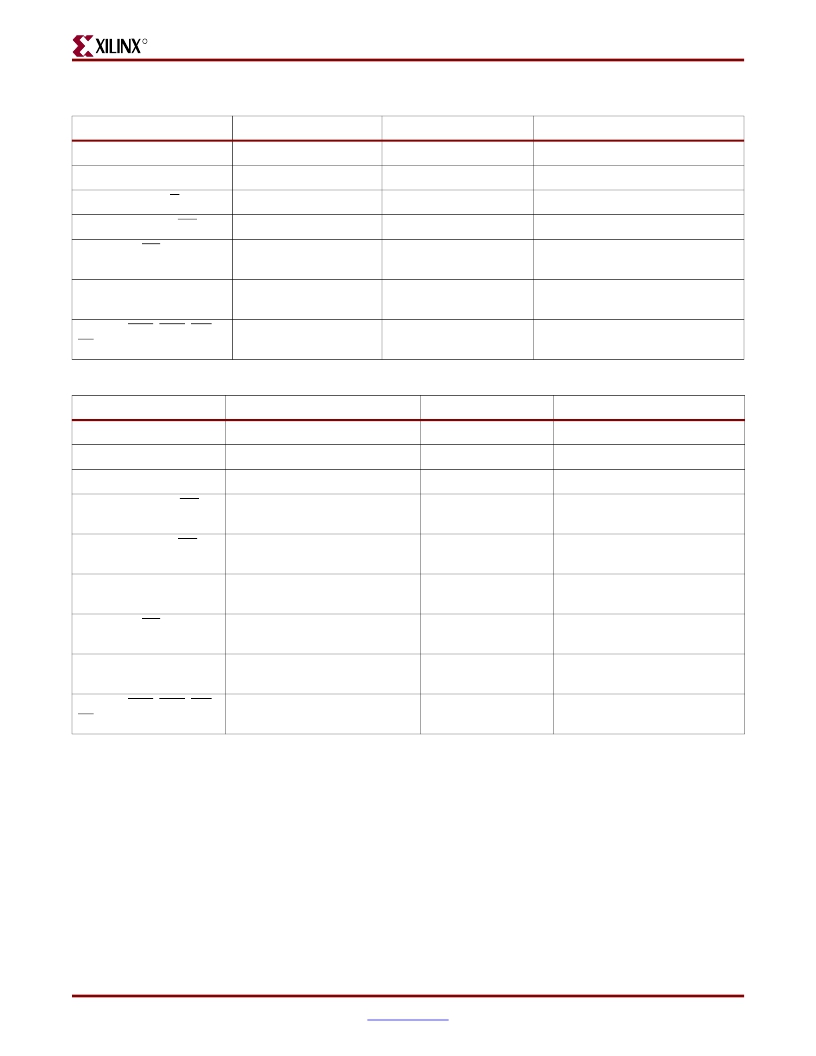

Table 5-4:

QDRII SRAM Terminations

Signal

Write Data (D)

Read Data (Q)

Write Strobe (K, K)

Read Strobe (CQ, CQ)

Clock (CK, CK)

FPGA Driver

HSTL_I_18

HSTL_I_DCI_18

HSTL_I_18

HSTL_I_DCI_18

HSTL_I_18

Termination at FPGA

No termination

No termination

No termination

No termination

No termination

Termination at Memory

50 Ω pull-up to 0.9V

No termination

50 Ω pull-up to 0.9V

No termination

100 Ω differential termination

between pair

Address (A, BA)

HSTL_I_18

No termination

50 Ω pull-up to 0.9V after the last

component

Control (RAS, CAS, WE,

CS, CKE, and BW)

HSTL_I_18

No termination

50 Ω pull-up to 0.9V after the last

component

Table 5-5:

RLDRAM II Terminations

Signal

Data (DQ for CIO)

Data (Q for SIO)

Write Data (D for SIO)

Write Strobe (DK, DK)

FPGA Driver

HSTL_II_DCI_18

HSTL_I_DCI_18

HSTL_I_18

DIFF_HSTL_I_18

Termination at FPGA

No termination

No termination

No termination

No termination

Termination at Memory

50 Ω pull-up to 0.9V

No termination

50 Ω pull-up to 0.9V

100 Ω differential termination

between pair

Read Strobe (QK, QK)

DIFF_HSTL_II_DCI_18 (for CIO)

No termination

No termination

DIFF_HSTL_I_DCI_18 (for SIO)

Data Valid (QVLD)

HSTL_II_DCI_18 (for CIO)

No termination

No termination

HSTL_I_DCI_18 (for SIO)

Clock (CK, CK)

DIFF_HSTL_I_18

No termination

100 Ω differential termination

between pair

Address (A, BA)

HSTL_I_18

No termination

50 Ω pull-up to 0.9V after the last

component

Control (RAS, CAS, WE,

CS, and CKE)

Virtex-5 FPGA ML561 User Guide

HSTL_I_18

No termination

50 Ω pull-up to 0.9V after the last

component

49

UG199 (v1.2.1) June 15, 2009

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

I-JET

JTAG ARM DEBUGGING PROBE

IAC24A

INPUT MODULE AC 5MA 24VDC

IAC5EQ

INPUT MODULE AC 10MA 5VDC

IB8RM

SURGE SUPP 8OUT 12'CORD W/REMOTE

IBAR12-20T

SURGE SUPPRSSR 20A 12OUT RACKMNT

IBAR12/20ULTRA

SURGE SUPPRSSR 20A 12OUT RACKMNT

IBAR12ULTRA

SURGE SUPPRSSR 15A 12OUT RACKMNT

IBAR12

SURGE SUPPRSSR 15A 12OUT RACKMNT

相关代理商/技术参数

HW-V5-ML561-UNI-G-J

功能描述:EVALUATION PLATFORM VIRTEX-5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-5 LXT 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-V5-PCIE2-UNI-G

功能描述:KIT DEV PCIEXPRESS GTX VIRTEX5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® -5 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-VID-KIT

功能描述:可编程逻辑 IC 开发工具 Lattice Video Interface Kit

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

HW-VL1

制造商:IDEC CORPORATION 功能描述:BARRIER

HW-VL2

制造商:IDEC Corporation 功能描述:COVER;HW FNGR SAFE CONTAC CVR 制造商:IDEC CORPORATION 功能描述:HW FNGR SAFE CONTAC CVR

HW-VL3

制造商:IDEC Corporation 功能描述: 制造商:IDEC Corporation 功能描述:Replacs TW-VL3 FNGR SAF

HWW-X030T-10015Z-H1

制造商:P-TEC 制造商全称:P-tec Corporation 功能描述:X30T RGB LED Wall Washers

HWW-X030T-10015Z-H2

制造商:P-TEC 制造商全称:P-tec Corporation 功能描述:X30T RGB LED Wall Washers